Cara membuat Pemancar UART serial sederhana di Verilog HDL

Kebanyakan Universal Asynchronous Receiver Transmitter (UART) yang saya temukan online, terlalu rumit dan sulit untuk dipahami, disini saya akan menjelaskan beberapa teori sederhana dan juga kode tentang cara membuatnya.

Pertama mari kita bicara tentang cara kerja pemancar. Prinsip dasarnya adalah mengirim beberapa bit data melalui satu baris. Di pemancar kami, data ini paralel, namun untuk mengurangi jumlah kabel yang diperlukan, kami menggunakan komunikasi serial yang diubah menjadi paralel di ujung penerima.

Hal-hal dasar yang kita butuhkan adalah sebagai berikut:

- Pembagi jam (penghitung kami)

Hal ini memungkinkan kita untuk mengirim data dengan kecepatan tertentu (baud rate). Penerima kami akan mengambil sampel dan mengambil data sedikit demi sedikit.

- Sebuah register geser

Kita perlu mengetahui berapa banyak bit pada suatu waktu yang kita transmisikan, register geser kita akan memiliki bit awal, bit data, bit paritas (opsional), bit akhir.

- Diagram keadaan

Sebelum menulis kode apa pun, kita harus memikirkan apa yang perlu kita buat dan cara terbaik adalah membuat diagram status dari desain kita. Kami tahu untuk pemancar kami membutuhkan 2 status, IDLE dan TRANSMITTING.

Setelah memiliki state diagram, sekarang kita dapat menghitung counter kita nantinya. Ini dilakukan dengan menggunakan:

penghitung = kecepatan jam FPGA/kecepatan baud

Dalam contoh ini saya menggunakan baud rate 9600, membuat penghitung saya = 5208.

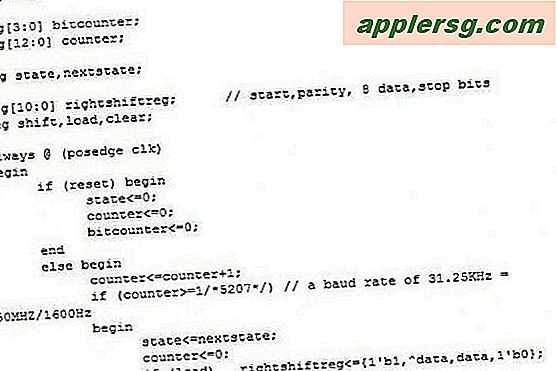

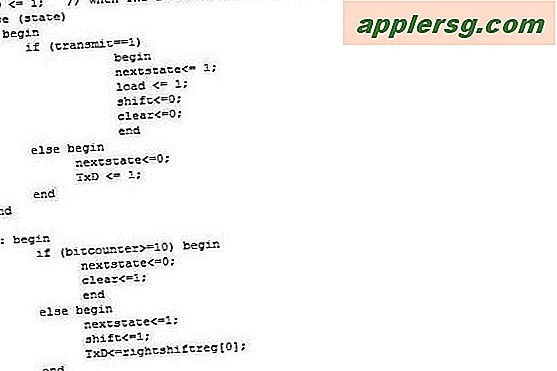

Terakhir, kami menghitung register geser kami dan menyelesaikan penulisan mesin negara kami. Dalam kode sampel saya, saya menggunakan bit awal, bit paritas, 8 bit data dan bit akhir. Ini adalah total 11 bit.

Kedua gambar pada langkah 2 dan 3 bersama-sama dalam modul yang sama melengkapi kode pemancar kami yang diperlukan untuk memprogram ke FPGA. Kode ini akan bekerja dengan FPGA lain yang terhubung secara serial atau dengan windows hyperterminal di antara perangkat keras lainnya. Dapat dengan mudah dimodifikasi untuk bekerja dengan lebih banyak lagi.

Terakhir, kami membuat perlengkapan uji untuk memperbaiki kesalahan dan mensimulasikan program kami sebelum memprogram FPGA.

Ini menyimpulkan Pemancar. Silakan tinggalkan komentar jika Anda memiliki pertanyaan atau merasa ada yang kurang di sini.

Tips

Baik transmitter maupun receiver harus mengetahui baud rate saat data sedang dikirim.